**LOONGSON**

# 龙芯 1C203 处理器用户手册

V1.0

2025 年 12 月

龙芯中科技术股份有限公司

自主决定命运，创新成就未来

北京市海淀区中关村环保科技示范园龙芯产业园 100095

Loongson Industrial Park. Zhongguancun Environmental Protection Park.

Haidian District, Beijing 100095. P.R.China

[www.loongson.cn](http://www.loongson.cn)

## 阅读指南

《龙芯 1C203 处理器用户手册》主要介绍龙芯 1C203 的架构与寄存器描述；包括用户手册和片上设备使用指南两部分，软件编程指南介绍软件开发过程中的常见问题。关于龙芯 1C203 处理器所集成的 LA132 处理器核的相关资料，请参阅《龙芯 LA132 处理器核用户手册》。

## 目 录

|                                       |          |

|---------------------------------------|----------|

| 目录 .....                              | i        |

| <b>第一章 概述 .....</b>                   | <b>1</b> |

| 1.1 特性 .....                          | 1        |

| 1.2 结构框图 .....                        | 2        |

| 1.3 文档约定 .....                        | 4        |

| 1.3.1 信号命名 .....                      | 4        |

| 1.3.2 信号类型 .....                      | 4        |

| 1.3.3 数值表示 .....                      | 4        |

| 1.3.4 寄存器域 .....                      | 4        |

| <b>第二章 地址空间 .....</b>                 | <b>5</b> |

| <b>第三章 ATIM 定时器 .....</b>             | <b>6</b> |

| 3.1 概述 .....                          | 6        |

| 3.2 功能描述 .....                        | 6        |

| 3.2.1 计数模式 .....                      | 6        |

| 3.2.2 输入模式 .....                      | 7        |

| 3.2.3 输出模式 .....                      | 8        |

| 3.2.4 定时器外部控制 .....                   | 10       |

| 3.3 寄存器空间 .....                       | 10       |

| 3.3.1 控制寄存器 1 (CR1) .....             | 11       |

| 3.3.2 控制寄存器 2 (CR2) .....             | 12       |

| 3.3.3 从模式控制寄存器 (SMCR) .....           | 13       |

| 3.3.4 DMA/中断使能寄存器 (DIER) .....        | 15       |

| 3.3.5 状态寄存器 (SR) .....                | 16       |

| 3.3.6 事件产生寄存器 (EGR) .....             | 17       |

| 3.3.7 捕获/比较模式寄存器 1(输出) (CCMR1) .....  | 18       |

| 3.3.8 捕获/比较模式寄存器 1(输入) (CCMR1) .....  | 20       |

| 3.3.9 捕获/比较模式寄存器 2(输出) (CCMR2) .....  | 21       |

| 3.3.10 捕获/比较模式寄存器 2(输入) (CCMR2) ..... | 22       |

|            |                                |           |

|------------|--------------------------------|-----------|

| 3.3.11     | 捕获/比较使能寄存器 (CCER) .....        | 23        |

| 3.3.12     | 计数器 (CNT) .....                | 24        |

| 3.3.13     | 预分频器 (PSC).....                | 25        |

| 3.3.14     | 自动重装载寄存器 (ARR).....            | 25        |

| 3.3.15     | 重复计数寄存器 (RCR) .....            | 25        |

| 3.3.16     | 捕获/比较寄存器 1 (CCR1) .....        | 26        |

| 3.3.17     | 捕获/比较寄存器 2 (CCR2) .....        | 26        |

| 3.3.18     | 捕获/比较寄存器 3 (CCR3).....         | 26        |

| 3.3.19     | 捕获/比较寄存器 4 (CCR4) .....        | 26        |

| 3.3.20     | 刹车和死区寄存器 (BDTR) .....          | 27        |

| 3.3.21     | 输入通道状态寄存器 (INSTA) .....        | 28        |

| 3.4        | 使用说明 .....                     | 28        |

| <b>第四章</b> | <b>GTIM 定时器 .....</b>          | <b>30</b> |

| 4.1        | 概述 .....                       | 30        |

| 4.2        | 功能描述 .....                     | 30        |

| 4.2.1      | 计数模式 .....                     | 30        |

| 4.2.2      | 输入模式 .....                     | 31        |

| 4.2.3      | 输出模式 .....                     | 32        |

| 4.2.4      | 定时器外部控制 .....                  | 33        |

| 4.3        | 寄存器空间 .....                    | 33        |

| 4.3.1      | 控制寄存器 1 (CR1) .....            | 34        |

| 4.3.2      | 控制寄存器 2 (CR2) .....            | 35        |

| 4.3.3      | 从模式控制寄存器 (SMCR) .....          | 36        |

| 4.3.4      | DMA/中断使能寄存器 (DIER) .....       | 37        |

| 4.3.5      | 状态寄存器 (SR) .....               | 38        |

| 4.3.6      | 事件产生寄存器 (EGR) .....            | 39        |

| 4.3.7      | 捕获/比较模式寄存器 1(输出) (CCMR1) ..... | 40        |

| 4.3.8      | 捕获/比较模式寄存器 1(输入) (CCMR1) ..... | 41        |

| 4.3.9      | 捕获/比较模式寄存器 2(输出) (CCMR2) ..... | 42        |

| 4.3.10     | 捕获/比较模式寄存器 2(输入) (CCMR2) ..... | 44        |

| 4.3.11     | 捕获/比较使能寄存器 (CCER) .....        | 45        |

|            |                          |           |

|------------|--------------------------|-----------|

| 4.3.12     | 计数器 (CNT) .....          | 46        |

| 4.3.13     | 预分频器 (PSC).....          | 46        |

| 4.3.14     | 自动重装载寄存器 (ARR).....      | 46        |

| 4.3.15     | 捕获/比较寄存器 1 (CCR1) .....  | 47        |

| 4.3.16     | 捕获/比较寄存器 2 (CCR2) .....  | 47        |

| 4.3.17     | 捕获/比较寄存器 3 (CCR3).....   | 47        |

| 4.3.18     | 捕获/比较寄存器 4 (CCR4) .....  | 47        |

| 4.3.19     | 输入通道状态寄存器 (INSTA) .....  | 48        |

| 4.4        | 使用说明 .....               | 48        |

| <b>第五章</b> | <b>BTIM 定时器 .....</b>    | <b>50</b> |

| 5.1        | 概述 .....                 | 50        |

| 5.2        | 功能描述 .....               | 50        |

| 5.3        | 寄存器空间 .....              | 50        |

| 5.3.1      | 控制寄存器 1 (CR1).....       | 51        |

| 5.3.2      | 控制寄存器 2 (CR2) .....      | 51        |

| 5.3.3      | DMA/中断使能寄存器 (DIER) ..... | 52        |

| 5.3.4      | 状态寄存器 (SR) .....         | 52        |

| 5.3.5      | 事件产生寄存器 (EGR) .....      | 52        |

| 5.3.6      | 计数器 (CNT) .....          | 53        |

| 5.3.7      | 预分频器 (PSC).....          | 53        |

| 5.3.8      | 自动重装载寄存器 (ARR) .....     | 53        |

| 5.4        | 使用说明 .....               | 54        |

| <b>第六章</b> | <b>ADC 控制器 .....</b>     | <b>55</b> |

| 6.1        | 概述 .....                 | 55        |

| 6.2        | 工作模式 .....               | 55        |

| 6.2.1      | 单次转换模式 .....             | 55        |

| 6.2.2      | 连续转换模式 .....             | 55        |

| 6.2.3      | 扫描模式 .....               | 55        |

| 6.2.4      | 间断模式 .....               | 55        |

| 6.3        | 功能描述 .....               | 56        |

| 6.3.1      | 注入通道管理 .....             | 56        |

|            |                                                        |           |

|------------|--------------------------------------------------------|-----------|

| 6.3.2      | 数据对齐 .....                                             | 56        |

| 6.3.3      | 可编程的通道采样时间 .....                                       | 56        |

| 6.3.4      | 模拟看门狗 .....                                            | 57        |

| 6.3.5      | DMA 请求 .....                                           | 57        |

| 6.3.6      | 外部触发 .....                                             | 57        |

| 6.4        | 寄存器定义 .....                                            | 57        |

| 6.4.1      | ADC 状态寄存器 (ADC_SR) .....                               | 58        |

| 6.4.2      | ADC 控制寄存器 1 (ADC_CR1) .....                            | 59        |

| 6.4.3      | ADC 控制寄存器 2 (ADC_CR2) .....                            | 60        |

| 6.4.4      | ADC 采样时间寄存器 1 (ADC_SMPR1) .....                        | 62        |

| 6.4.5      | ADC 采样时间寄存器 2 (ADC_SMPR2) .....                        | 63        |

| 6.4.6      | ADC 输入通道数据偏移寄存器 (ADC_JOFR <sub>x</sub> (x=1..4)) ..... | 63        |

| 6.4.7      | ADC 看门狗高阈值寄存器 (ADC_HTR) .....                          | 63        |

| 6.4.8      | ADC 看门狗低阈值寄存器 (ADC_LTR) .....                          | 63        |

| 6.4.9      | ADC 规则序列寄存器 1 (ADC_SQR1) .....                         | 64        |

| 6.4.10     | ADC 规则序列寄存器 2 (ADC_SQR2) .....                         | 65        |

| 6.4.11     | ADC 规则序列寄存器 3 (ADC_SQR3) .....                         | 65        |

| 6.4.12     | ADC 注入序列寄存器 (ADC_JSQR) .....                           | 66        |

| 6.4.13     | ADC 注入数据寄存器 (ADC_JDR <sub>x</sub> (x=1..4)) .....      | 67        |

| 6.4.14     | ADC 规则数据寄存器 (ADC_DR) .....                             | 67        |

| 6.5        | 使用说明 .....                                             | 68        |

| <b>第七章</b> | <b>DMA 控制器 .....</b>                                   | <b>69</b> |

| 7.1        | 概述 .....                                               | 69        |

| 7.2        | 寄存器定义 .....                                            | 69        |

| 7.2.1      | DMA 中断状态寄存器 (DMA_ISR) .....                            | 70        |

| 7.2.2      | DMA 中断标志清除寄存器 (DMA_IFCR) .....                         | 70        |

| 7.2.3      | DMA 通道 x 配置寄存器 (DMA_CCR <sub>x</sub> ) .....           | 70        |

| 7.2.4      | DMA 通道 x 传输数量寄存器 (DMA_CNDTR <sub>x</sub> ) .....       | 72        |

| 7.2.5      | DMA 通道 x 外设地址寄存器 (DMA_CPAR <sub>x</sub> ) .....        | 72        |

| 7.2.6      | DMA 通道 x 存储器地址寄存器 (DMA_CMAR <sub>x</sub> ) .....       | 72        |

| 7.3        | 功能描述 .....                                             | 73        |

|            |                       |    |

|------------|-----------------------|----|

| 7.3.1      | 配置流程                  | 73 |

| 7.3.2      | 宽度和对齐方式               | 73 |

| 7.3.3      | 通道映射                  | 73 |

| <b>第八章</b> | <b>CRC 控制器</b>        | 75 |

| 8.1        | 概述                    | 75 |

| 8.2        | 寄存器定义                 | 75 |

| 8.2.1      | CRC 数据寄存器 (CRC_DR)    | 75 |

| 8.2.2      | CRC 独立数据寄存器 (CRC_IDR) | 76 |

| 8.2.3      | CRC 控制寄存器 (CRC_CR)    | 76 |

| <b>第九章</b> | <b>Flash</b>          | 77 |

| 9.1        | 概述                    | 77 |

| 9.2        | 存储空间                  | 77 |

| 9.3        | 寄存器空间                 | 78 |

| 9.3.1      | 命令寄存器 (CMD)           | 78 |

| 9.3.2      | 状态寄存器 (STS)           | 78 |

| 9.3.3      | 擦写时间寄存器 (PET)         | 79 |

| 9.3.4      | BOUND 寄存器 (BOUND)     | 79 |

| 9.3.5      | OTP 配置寄存器 (OTP_CFG)   | 80 |

| 9.4        | 使用说明                  | 80 |

| 9.4.1      | 代码保护                  | 80 |

| 9.4.2      | 中断                    | 80 |

| 9.4.3      | 编程指南                  | 80 |

| 9.4.4      | OTP 功能                | 81 |

| <b>第十章</b> | <b>SPI 控制器</b>        | 82 |

| 10.1       | 概述                    | 82 |

| 10.2       | 寄存器定义                 | 82 |

| 10.2.1     | 控制寄存器 (SPCR)          | 83 |

| 10.2.2     | 状态寄存器 (SPSR)          | 83 |

| 10.2.3     | 数据寄存器 (DATA)          | 84 |

| 10.2.4     | 外部寄存器 (SPER)          | 84 |

| 10.2.5     | 参数控制寄存器 (PARAM)       | 85 |

|                                        |           |

|----------------------------------------|-----------|

| 10.2.6 片选控制寄存器 (SOFTCS) .....          | 85        |

| 10.2.7 Flash 读引擎时序控制寄存器 (TIMING) ..... | 86        |

| 10.3 接口时序 .....                        | 86        |

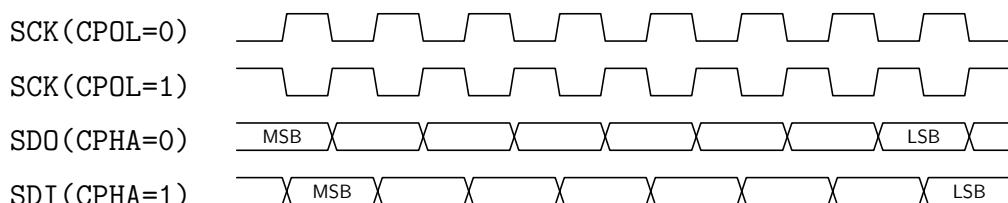

| 10.3.1 SPI 主控制器接口时序 .....              | 86        |

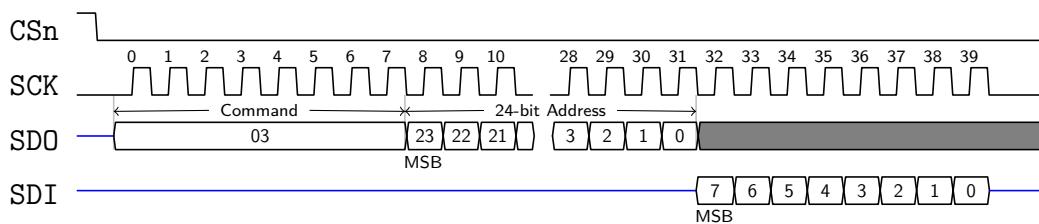

| 10.3.2 SPI Flash 访问时序 .....            | 86        |

| 10.4 使用指南 .....                        | 86        |

| 10.4.1 SPI 主控制器的读写操作 .....             | 86        |

| 10.4.2 硬件 SPI Flash 读 .....            | 88        |

| 10.4.3 混合访问 SPI Flash 和 SPI 主控制器 ..... | 88        |

| 10.4.4 安装模式 .....                      | 88        |

| <b>第十一章 UART 控制器 .....</b>             | <b>89</b> |

| 11.1 概述 .....                          | 89        |

| 11.2 寄存器定义 .....                       | 89        |

| 11.2.1 数据寄存器 (DAT) .....               | 89        |

| 11.2.2 中断使能寄存器 (IER) .....             | 89        |

| 11.2.3 中断状态寄存器 (IIR) .....             | 90        |

| 11.2.4 FIFO 控制寄存器 (FCR) .....          | 90        |

| 11.2.5 线路控制寄存器 (LCR) .....             | 91        |

| 11.2.6 MODEM 控制寄存器 (MCR) .....         | 92        |

| 11.2.7 线路状态寄存器 (LSR) .....             | 92        |

| 11.2.8 分频值低字节寄存器 (DL_L) .....          | 93        |

| 11.2.9 分频值高字节寄存器 (DL_H) .....          | 93        |

| 11.2.10 分频值小数寄存器 (DL_D) .....          | 93        |

| 11.3 使用指南 .....                        | 94        |

| 11.3.1 配置流程 .....                      | 94        |

| <b>第十二章 I<sup>2</sup>C 控制器 .....</b>   | <b>95</b> |

| 12.1 概述 .....                          | 95        |

| 12.2 主要特性 .....                        | 95        |

| 12.3 功能描述 .....                        | 96        |

| 12.3.1 模式选择 .....                      | 96        |

| 12.3.2 从模式 .....                       | 96        |

|                                                   |     |

|---------------------------------------------------|-----|

| 12.3.3 主模式 .....                                  | 98  |

| 12.3.4 错误条件 .....                                 | 102 |

| 12.3.5 DMA 请求 .....                               | 102 |

| 12.4 中断 .....                                     | 103 |

| 12.5 寄存器定义 .....                                  | 104 |

| 12.5.1 I <sup>2</sup> C 控制寄存器 1 (I2C_CR1) .....   | 104 |

| 12.5.2 I <sup>2</sup> C 控制寄存器 2 (I2C_CR2) .....   | 105 |

| 12.5.3 I <sup>2</sup> C 从地址寄存器 (I2C_OAR) .....    | 106 |

| 12.5.4 I <sup>2</sup> C 数据寄存器 (I2C_DR) .....      | 106 |

| 12.5.5 I <sup>2</sup> C 状态寄存器 1 (I2C_SR1) .....   | 106 |

| 12.5.6 I <sup>2</sup> C 状态寄存器 2 (I2C_SR2) .....   | 108 |

| 12.5.7 I <sup>2</sup> C 时钟控制寄存器 (I2C_CCR) .....   | 108 |

| 12.5.8 I <sup>2</sup> C 上升时间寄存器 (I2C_TRISE) ..... | 109 |

| <b>第十三章 CAN FD 控制器 .....</b>                      | 110 |

| 13.1 概述 .....                                     | 110 |

| 13.2 CAN FD 控制器特性 .....                           | 110 |

| <b>第十四章 模拟比较器 .....</b>                           | 111 |

| 14.1 概述 .....                                     | 111 |

| 14.2 寄存器空间 .....                                  | 111 |

| 14.2.1 比较器 x 控制寄存器 (CRx) .....                    | 111 |

| 14.2.2 状态寄存器 (SR) .....                           | 112 |

| <b>第十五章 CONF .....</b>                            | 113 |

| 15.1 概述 .....                                     | 113 |

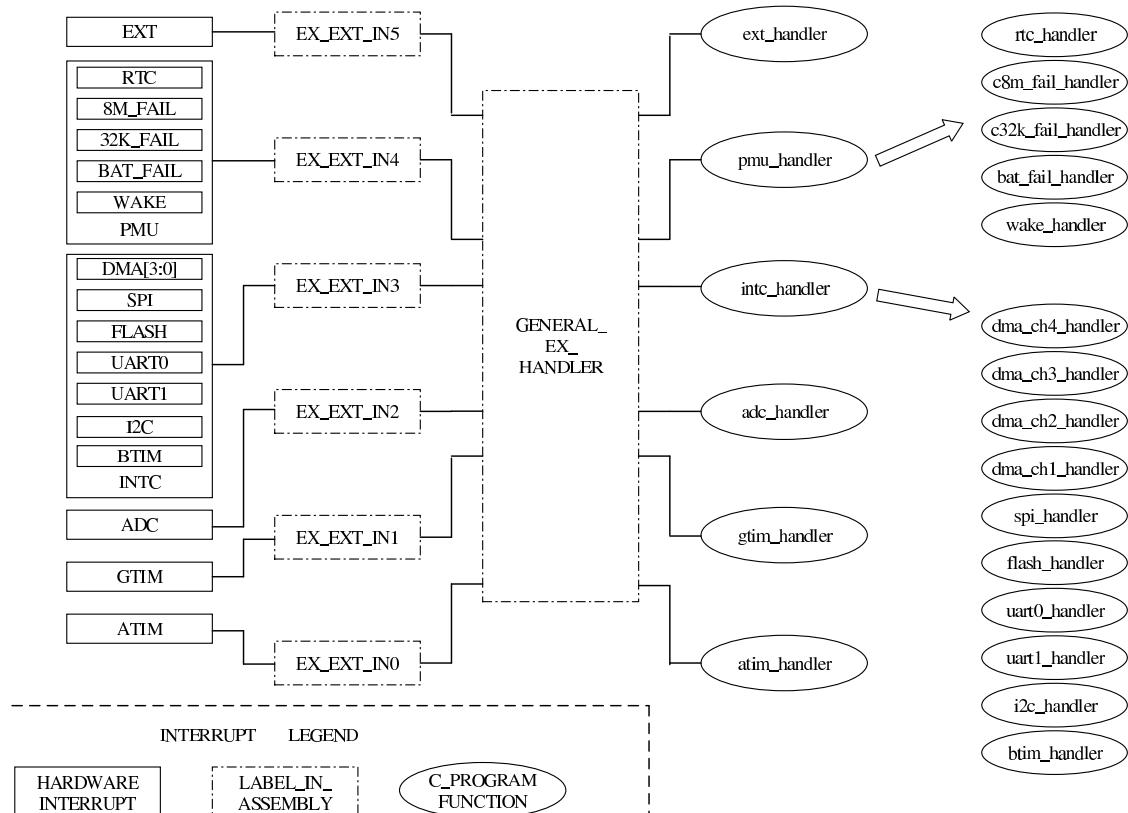

| 15.2 中断结构 .....                                   | 113 |

| 15.3 中断处理 .....                                   | 114 |

| 15.4 寄存器定义 .....                                  | 114 |

| 15.4.1 中断使能寄存器 (INT_EN) .....                     | 115 |

| 15.4.2 中断输出寄存器 (INT_OUT) .....                    | 115 |

| 15.4.3 CPU 全局配置 (CpuCtrl) .....                   | 116 |

| 15.4.4 软件复位 (RstCtrl) .....                       | 117 |

| 15.4.5 时钟关断 (ClkCtrl) .....                       | 118 |

|                                      |            |

|--------------------------------------|------------|

| 15.4.6 运行状态及保护寄存器 (SrProt) .....     | 119        |

| 15.4.7 OSC TRIM 寄存器 (OSCTrim) .....  | 119        |

| 15.4.8 PLL 控制寄存器 (PllCtrl) .....     | 119        |

| <b>第十六章 电源与顶层控制 .....</b>            | <b>121</b> |

| 16.1 电源管理 .....                      | 121        |

| 16.2 寄存器定义 .....                     | 122        |

| 16.2.1 芯片全局配置 (ChipCtrl) .....       | 122        |

| 16.2.2 命令与状态 (CmdSts) .....          | 123        |

| 16.2.3 时间计数器 (Count) .....           | 124        |

| 16.2.4 唤醒时间配置 (Compare) .....        | 124        |

| 16.2.5 软件复位 (RstCtrl) .....          | 124        |

| 16.2.6 时钟关断 (ClkCtrl) .....          | 124        |

| 16.2.7 看门狗配置寄存器 (WdtCfg) .....       | 125        |

| 16.2.8 看门狗重置寄存器 (WdtFeed) .....      | 125        |

| 16.2.9 电源配置 (PowerCfg) .....         | 126        |

| 16.2.10 命令写端口 (CommandW) .....       | 126        |

| 16.2.11 用户数据 0/1/2/3 (UserDat) ..... | 126        |

| <b>第十七章 实时时钟 .....</b>               | <b>128</b> |

| 17.1 概述 .....                        | 128        |

| 17.2 寄存器定义 .....                     | 128        |

| 17.2.1 分频值寄存器 (FREQ) .....           | 128        |

| 17.2.2 配置寄存器 (CFG) .....             | 128        |

| 17.2.3 时间值寄存器 0 (RTC0) .....         | 129        |

| 17.2.4 时间值寄存器 1 (RTC1) .....         | 129        |

| 17.3 说明 .....                        | 130        |

| <b>第十八章 IO 配置 .....</b>              | <b>131</b> |

| 18.1 概述 .....                        | 131        |

| 18.2 寄存器定义 .....                     | 132        |

| 18.2.1 引脚复用选择 (IOSEL0) .....         | 133        |

| 18.2.2 引脚复用选择 (IOSEL1) .....         | 133        |

| 18.2.3 外部触发使能 (ExtEn) .....          | 133        |

---

|         |                                  |     |

|---------|----------------------------------|-----|

| 18.2.4  | 外部中断使能 (ExintEn) .....           | 134 |

| 18.2.5  | 外部中断极性 (ExintPol) .....          | 134 |

| 18.2.6  | 外部中断上升沿 (ExintRis) .....         | 134 |

| 18.2.7  | 外部中断下降沿 (ExintFal) .....         | 134 |

| 18.2.8  | 外部触发状态 (ExtSrc) .....            | 135 |

| 18.2.9  | 端口配置低寄存器 (GPIOx_CRL) .....       | 135 |

| 18.2.10 | 端口配置高寄存器 (GPIOx_CRH) .....       | 136 |

| 18.2.11 | 端口输入数据寄存器 (GPIOx_IDR) .....      | 136 |

| 18.2.12 | 端口输出数据寄存器 (GPIOx_ODR) .....      | 136 |

| 18.2.13 | 端口设置/清除寄存器 (GPIOx_BSRR) .....    | 137 |

| 18.2.14 | GPIO 位访问配置端口 (GPIOBit_CFG) ..... | 137 |

| 18.2.15 | GPIO 位访问输入端口 (GPIOBit_IDR) ..... | 137 |

| 18.2.16 | GPIO 位访问输出端口 (GPIOBit_ODR) ..... | 138 |

## 表 目 录

|      |                        |    |

|------|------------------------|----|

| 1.1  | 信号类型约定 .....           | 4  |

| 2.1  | 地址空间分布 .....           | 5  |

| 3.1  | ATIM 控制器寄存器列表 .....    | 10 |

| 3.2  | 控制寄存器 1 .....          | 11 |

| 3.3  | 控制寄存器 2 .....          | 12 |

| 3.4  | 从模式控制寄存器 .....         | 13 |

| 3.5  | DMA/中断使能寄存器 .....      | 15 |

| 3.6  | 状态寄存器 .....            | 16 |

| 3.7  | 事件产生寄存器 .....          | 17 |

| 3.8  | 捕获/比较模式寄存器 1(输出) ..... | 18 |

| 3.9  | 捕获/比较模式寄存器 1(输入) ..... | 20 |

| 3.10 | 捕获/比较模式寄存器 2(输出) ..... | 21 |

| 3.11 | 捕获/比较模式寄存器 2(输入) ..... | 22 |

| 3.12 | 捕获/比较使能寄存器 .....       | 24 |

| 3.13 | 计数器 .....              | 25 |

| 3.14 | 预分频器 .....             | 25 |

| 3.15 | 自动重装载寄存器 .....         | 25 |

| 3.16 | 重复计数寄存器 .....          | 25 |

| 3.17 | 捕获/比较寄存器 1 .....       | 26 |

| 3.18 | 捕获/比较寄存器 2 .....       | 26 |

| 3.19 | 捕获/比较寄存器 3 .....       | 26 |

| 3.20 | 捕获/比较寄存器 4 .....       | 27 |

| 3.21 | 刹车和死区寄存器 .....         | 27 |

| 3.22 | 输入通道状态寄存器 .....        | 28 |

| 4.1  | GTIM 控制器寄存器列表 .....    | 33 |

| 4.2  | 控制寄存器 1 .....          | 34 |

|      |                        |    |

|------|------------------------|----|

| 4.3  | 控制寄存器 2 .....          | 35 |

| 4.4  | 从模式控制寄存器 .....         | 36 |

| 4.5  | DMA/中断使能寄存器 .....      | 37 |

| 4.6  | 状态寄存器 .....            | 38 |

| 4.7  | 事件产生寄存器 .....          | 39 |

| 4.8  | 捕获/比较模式寄存器 1(输出) ..... | 40 |

| 4.9  | 捕获/比较模式寄存器 1(输入) ..... | 41 |

| 4.10 | 捕获/比较模式寄存器 2(输出) ..... | 43 |

| 4.11 | 捕获/比较模式寄存器 2(输入) ..... | 44 |

| 4.12 | 捕获/比较使能寄存器 .....       | 45 |

| 4.13 | 计数器 .....              | 46 |

| 4.14 | 预分频器 .....             | 46 |

| 4.15 | 自动重装载寄存器 .....         | 46 |

| 4.16 | 捕获/比较寄存器 1 .....       | 47 |

| 4.17 | 捕获/比较寄存器 2 .....       | 47 |

| 4.18 | 捕获/比较寄存器 3 .....       | 47 |

| 4.19 | 捕获/比较寄存器 4 .....       | 48 |

| 4.20 | 输入通道状态寄存器 .....        | 48 |

| 5.1  | BTIM 控制器寄存器列表 .....    | 50 |

| 5.2  | 控制寄存器 1 .....          | 51 |

| 5.3  | 控制寄存器 2 .....          | 52 |

| 5.4  | DMA/中断使能寄存器 .....      | 52 |

| 5.5  | 状态寄存器 .....            | 52 |

| 5.6  | 事件产生寄存器 .....          | 53 |

| 5.7  | 计数器 .....              | 53 |

| 5.8  | 预分频器 .....             | 53 |

| 5.9  | 自动重装载寄存器 .....         | 53 |

| 6.1  | ADC 控制器寄存器列表 .....     | 58 |

| 6.2  | ADC 状态寄存器 .....        | 58 |

| 6.3  | ADC 控制寄存器 1 .....      | 59 |

|      |                         |    |

|------|-------------------------|----|

| 6.4  | ADC 控制寄存器 2 .....       | 60 |

| 6.5  | ADC 采样时间寄存器 1 .....     | 62 |

| 6.6  | ADC 采样时间寄存器 2 .....     | 63 |

| 6.7  | ADC 输入通道数据偏移寄存器 .....   | 63 |

| 6.8  | ADC 看门狗高阈值寄存器 .....     | 63 |

| 6.9  | ADC 看门狗低阈值寄存器 .....     | 64 |

| 6.10 | ADC 规则序列寄存器 1 .....     | 64 |

| 6.11 | ADC 规则序列寄存器 2 .....     | 65 |

| 6.12 | ADC 规则序列寄存器 3 .....     | 65 |

| 6.13 | ADC 注入序列寄存器 .....       | 66 |

| 6.14 | ADC 注入数据寄存器 .....       | 67 |

| 6.15 | ADC 规则数据寄存器 .....       | 67 |

| 7.1  | DMA 寄存器列表 .....         | 69 |

| 7.2  | DMA 中断状态寄存器 .....       | 70 |

| 7.3  | DMA 中断标志清除寄存器 .....     | 70 |

| 7.4  | DMA 通道 x 配置寄存器 .....    | 71 |

| 7.5  | DMA 通道 x 传输数量寄存器 .....  | 72 |

| 7.6  | DMA 通道 x 外设地址寄存器 .....  | 72 |

| 7.7  | DMA 通道 x 存储器地址寄存器 ..... | 73 |

| 7.8  | DMA 通道与外设请求对应关系 .....   | 73 |

| 8.1  | CRC 寄存器列表 .....         | 75 |

| 8.2  | CRC 数据寄存器 .....         | 75 |

| 8.3  | CRC 独立数据寄存器 .....       | 76 |

| 8.4  | CRC 控制寄存器 .....         | 76 |

| 9.1  | Flash 控制器寄存器列表 .....    | 78 |

| 9.2  | 命令寄存器 .....             | 78 |

| 9.3  | 状态寄存器 .....             | 78 |

| 9.4  | 擦写时间寄存器 .....           | 79 |

| 9.5  | BOUND 寄存器 .....         | 79 |

| 9.6  | OTP 配置寄存器 .....         | 80 |

|       |                                 |     |

|-------|---------------------------------|-----|

| 10.1  | SPI 控制器寄存器列表 .....              | 82  |

| 10.2  | 控制寄存器 .....                     | 83  |

| 10.3  | 状态寄存器 .....                     | 83  |

| 10.4  | 数据寄存器 .....                     | 84  |

| 10.5  | 外部寄存器 .....                     | 84  |

| 10.6  | SPI 分频系数 .....                  | 84  |

| 10.7  | 参数控制寄存器 .....                   | 85  |

| 10.8  | 片选控制寄存器 .....                   | 85  |

| 10.9  | Flash 读引擎时序控制寄存器 .....          | 86  |

| 11.1  | UART 寄存器列表 .....                | 89  |

| 11.2  | 数据寄存器 .....                     | 89  |

| 11.3  | 中断使能寄存器 .....                   | 90  |

| 11.4  | 中断状态寄存器 .....                   | 90  |

| 11.5  | 中断控制器功能表 .....                  | 90  |

| 11.6  | FIFO 控制寄存器 .....                | 91  |

| 11.7  | 线路控制寄存器 .....                   | 91  |

| 11.8  | MODEM 控制寄存器 .....               | 92  |

| 11.9  | 线路状态寄存器 .....                   | 92  |

| 11.10 | 分频值低字节寄存器 .....                 | 93  |

| 11.11 | 分频值高字节寄存器 .....                 | 93  |

| 11.12 | 分频值小数寄存器 .....                  | 93  |

| 12.1  | I <sup>2</sup> C 中断请求 .....     | 103 |

| 12.2  | I <sup>2</sup> C 控制器寄存器列表 ..... | 104 |

| 12.3  | I <sup>2</sup> C 控制寄存器 1 .....  | 104 |

| 12.4  | I <sup>2</sup> C 控制寄存器 2 .....  | 105 |

| 12.5  | I <sup>2</sup> C 从地址寄存器 .....   | 106 |

| 12.6  | I <sup>2</sup> C 数据寄存器 .....    | 106 |

| 12.7  | I <sup>2</sup> C 状态寄存器 1 .....  | 106 |

| 12.8  | I <sup>2</sup> C 状态寄存器 2 .....  | 108 |

| 12.9  | I <sup>2</sup> C 时钟控制寄存器 .....  | 108 |

|                                      |     |

|--------------------------------------|-----|

| 12.10 I <sup>2</sup> C 上升时间寄存器 ..... | 109 |

| 14.1 ACOMP 控制器寄存器列表 .....            | 111 |

| 14.2 比较器 x 控制寄存器 .....               | 111 |

| 14.3 状态寄存器 .....                     | 112 |

| 15.1 中断对应关系 .....                    | 113 |

| 15.2 Conf 寄存器列表 .....                | 115 |

| 15.3 中断使能寄存器 .....                   | 115 |

| 15.4 中断输出寄存器 .....                   | 115 |

| 15.5 CPU 全局配置 .....                  | 116 |

| 15.6 软件复位 .....                      | 117 |

| 15.7 时钟关断 .....                      | 118 |

| 15.8 运行状态及保护寄存器 .....                | 119 |

| 15.9 OSC TRIM 寄存器 .....              | 119 |

| 15.10 PLL 控制寄存器 .....                | 120 |

| 16.1 PMU 寄存器列表 .....                 | 122 |

| 16.2 芯片全局配置 .....                    | 122 |

| 16.3 命令与状态 .....                     | 123 |

| 16.4 时间计数器 .....                     | 124 |

| 16.5 唤醒时间配置 .....                    | 124 |

| 16.6 软件复位 .....                      | 124 |

| 16.7 时钟关断 .....                      | 125 |

| 16.8 看门狗配置寄存器 .....                  | 125 |

| 16.9 看门狗重置寄存器 .....                  | 126 |

| 16.10 电源配置 .....                     | 126 |

| 16.11 命令写端口 .....                    | 126 |

| 16.12 用户数据 0/1/2/3 .....             | 127 |

| 17.1 实时时钟寄存器列表 .....                 | 128 |

| 17.2 分频值寄存器 .....                    | 128 |

| 17.3 配置寄存器 .....                     | 129 |

|       |                    |     |

|-------|--------------------|-----|

| 17.4  | 时间值寄存器 0 .....     | 129 |

| 17.5  | 时间值寄存器 1 .....     | 130 |

| 18.1  | QFN32 引脚复用关系 ..... | 131 |

| 18.2  | AFIO 寄存器列表 .....   | 132 |

| 18.3  | EXTI 寄存器列表 .....   | 132 |

| 18.4  | GPIOA 寄存器列表 .....  | 132 |

| 18.5  | GPIOB 寄存器列表 .....  | 133 |

| 18.6  | 引脚复用选择 .....       | 133 |

| 18.7  | 引脚复用选择 .....       | 133 |

| 18.8  | 外部触发使能 .....       | 134 |

| 18.9  | 外部中断使能 .....       | 134 |

| 18.10 | 外部中断极性 .....       | 134 |

| 18.11 | 外部中断上升沿 .....      | 134 |

| 18.12 | 外部中断下降沿 .....      | 135 |

| 18.13 | 外部触发状态 .....       | 135 |

| 18.14 | 端口配置低寄存器 .....     | 135 |

| 18.15 | 端口配置高寄存器 .....     | 136 |

| 18.16 | 端口输入数据寄存器 .....    | 136 |

| 18.17 | 端口输出数据寄存器 .....    | 137 |

| 18.18 | 端口设置/清除寄存器 .....   | 137 |

| 18.19 | GPIO 位访问配置端口 ..... | 137 |

| 18.20 | GPIO 位访问输入端口 ..... | 138 |

| 18.21 | GPIO 位访问输出端口 ..... | 138 |

## 图 目 录

|                                 |     |

|---------------------------------|-----|

| 1.1 龙芯 1C203 结构图 .....          | 3   |

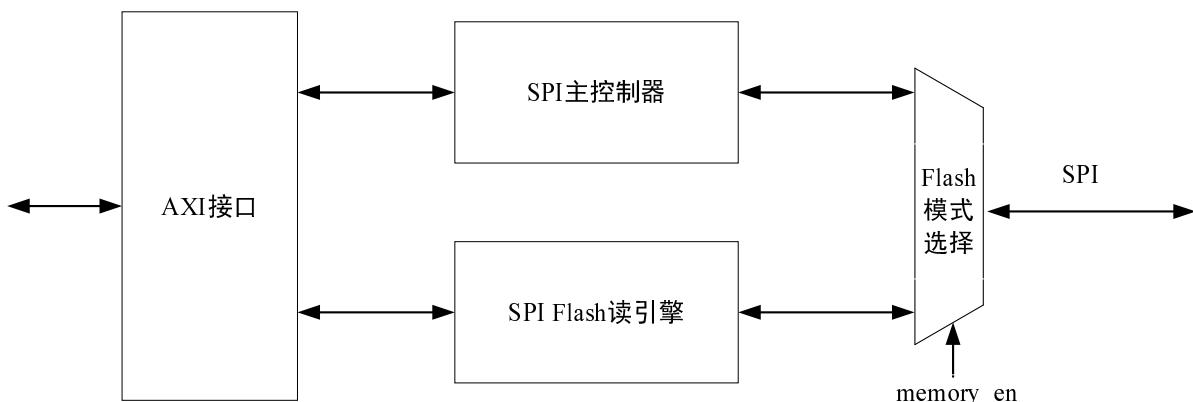

| 10.1 SPI 模块结构 .....             | 82  |

| 10.2 SPI 主控制器接口时序 .....         | 86  |

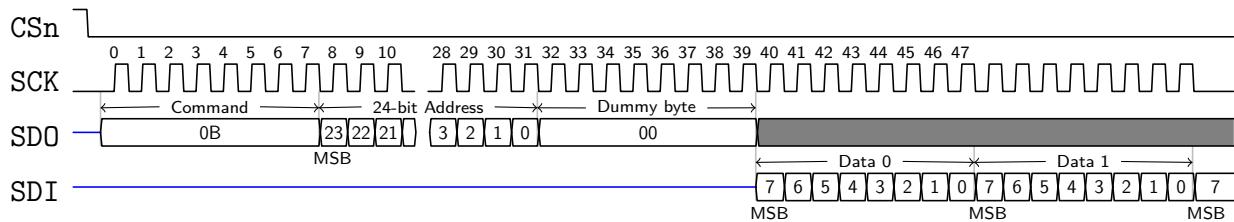

| 10.3 SPI Flash 标准读时序 .....      | 87  |

| 10.4 SPI Flash 快速读时序 .....      | 87  |

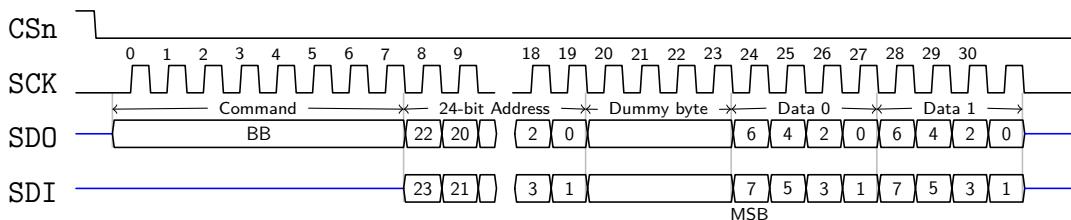

| 10.5 SPI Flash 双向 I/O 读时序 ..... | 87  |

| 12.1 从发送模式示意图 .....             | 97  |

| 12.2 从接收模式示意图 .....             | 97  |

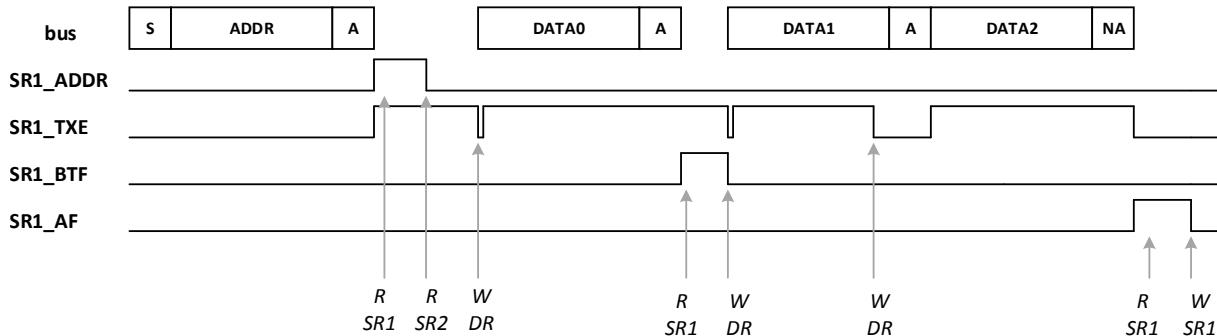

| 12.3 主发送模式示意图 .....             | 99  |

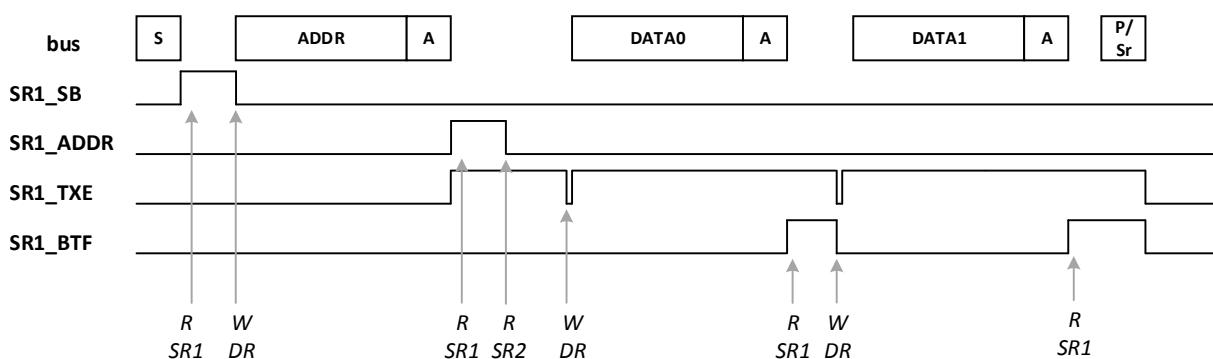

| 12.4 主接收模式（及时）示意图 .....         | 101 |

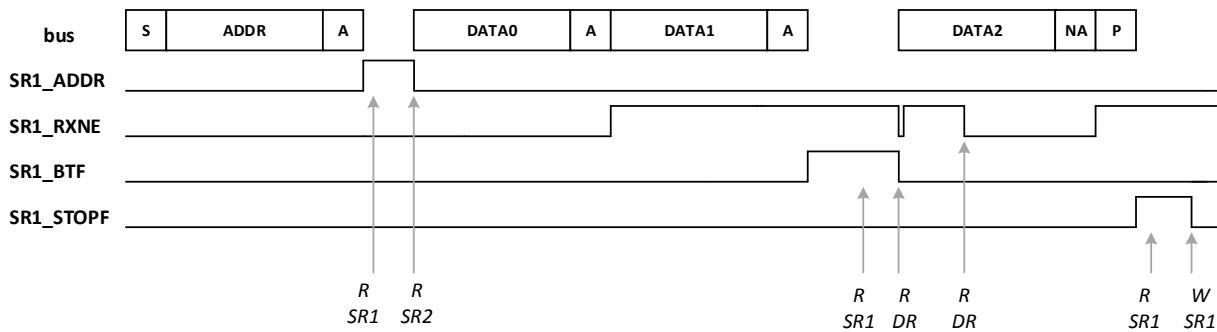

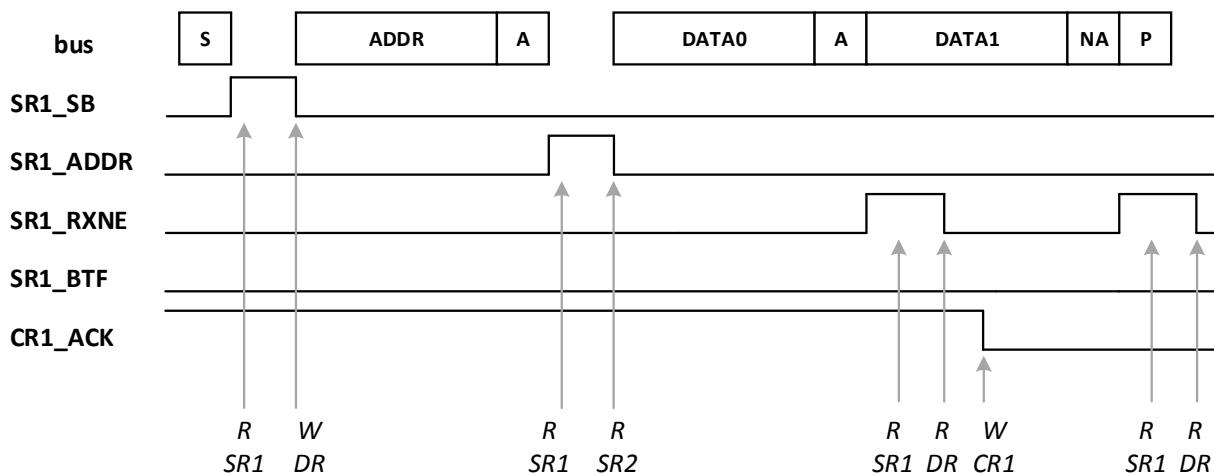

| 12.5 主接收模式（非及时、3 字节）示意图 .....   | 101 |

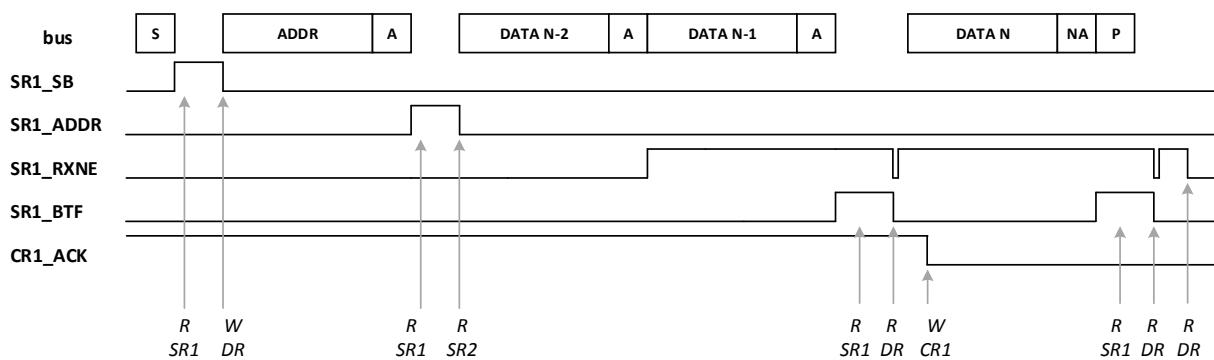

| 12.6 主接收模式（非及时、2 字节）示意图 .....   | 101 |

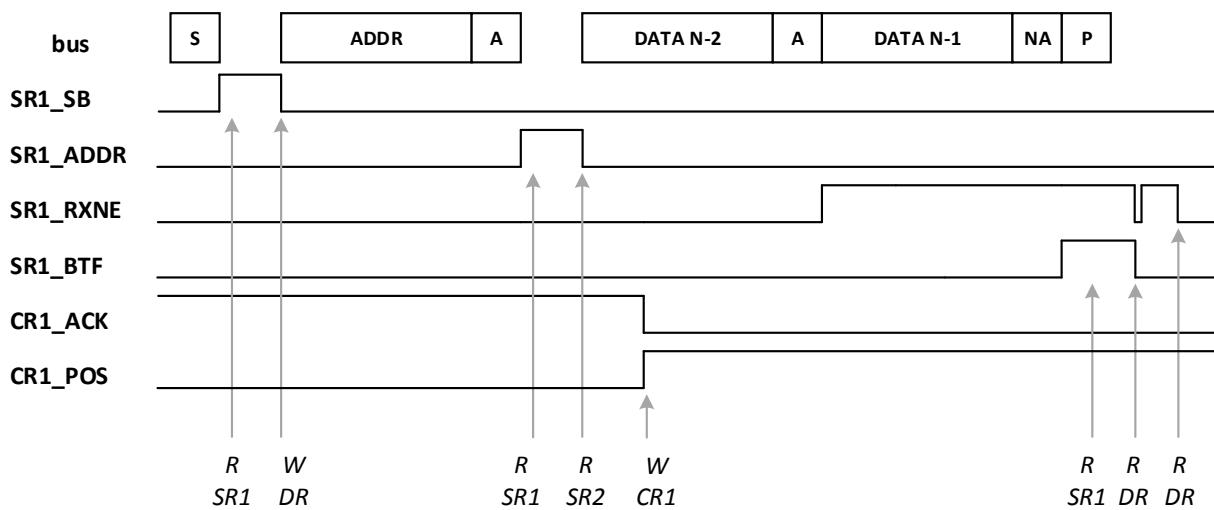

| 15.1 中断连接示意 .....               | 113 |

| 16.1 电源架构 .....                 | 121 |

## 第一章 概述

龙芯 1C203 是针对电机驱动应用而设计的微控制器芯片。该芯片集成 CPU、SRAM、Flash、PMU、ATIM、GTIM、BTIM、ADC、DMA、SPI、UART、I<sup>2</sup>C、RTC 等功能模块，具备驱动舵机、有刷电机、无刷电机 PWM 的原生支持，同时具备常见通信模块，可以满足高性价比的常见电机应用。

### 1.1 特性

龙芯 1C203 具有以下关键特性：

- LA132 处理器核

- 32 位单发射

- 顺序执行、三级流水

- 无 cache、MMU

- JTAG 调试接口支持断点、单步

- 8KB 指令 SRAM、8KB 数据 SRAM

- 主频最高 160MHz

- 片上 Flash

- 128KB 容量

- 每页 256 字节

- 定时器

- BTIM,GTIM,ATIM 三种定时器

- 支持 PWM 可调输出，输入捕获

- 调试模式下暂停

- ADC

- 10 路输入

- 12 位分辨率

- 最高采样率 937KSPS

- ACOMP

- 3 通道模拟比较器

- DMA

- 4 个通道

- 支持存储器到存储器，存储器到设备和设备到存储器传输

- 支持循环传输

- 支持以 1/2/4 字节为单位传输

- SPI 控制器

- 独立的 Flash 接口，支持启动

- UART 控制器

- 2 路两线串口

- I<sup>2</sup>C 控制器

- 1 路

- 支持主从模式

- 速率 100/400Kbps

- CAN-FD 控制器

- 1 路 CAN-FD

- 看门狗

- 上电默认开启

- 调试模式下暂停

- GPIO

- 29 路复用 GPIO

- 上电默认为 GPIO 功能，高阻态

- 低功耗

- CPU 域可关断

- APB 模块独立的时钟门控开关

## 1.2 结构框图

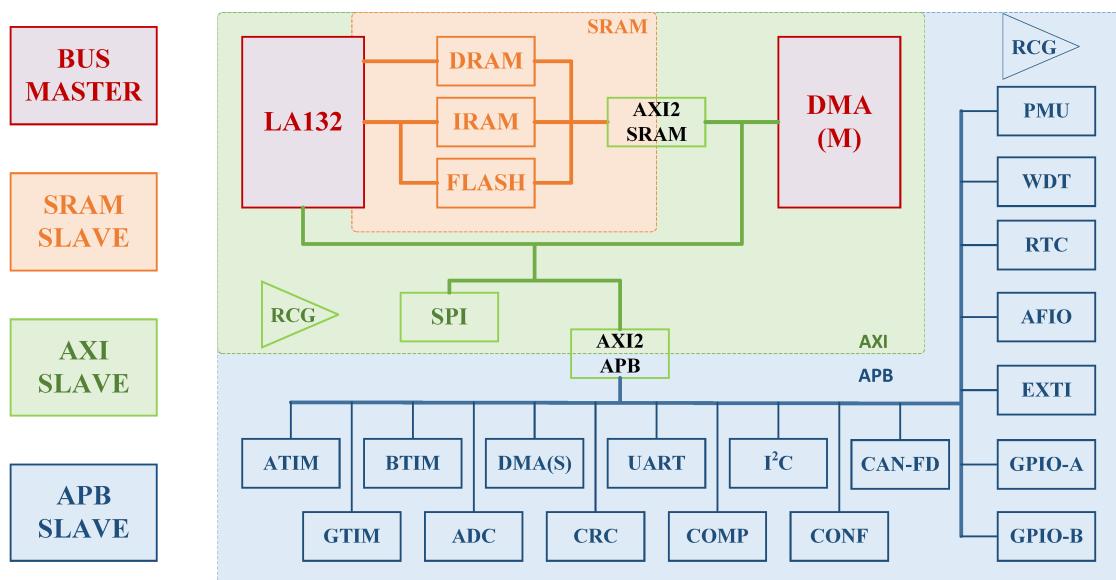

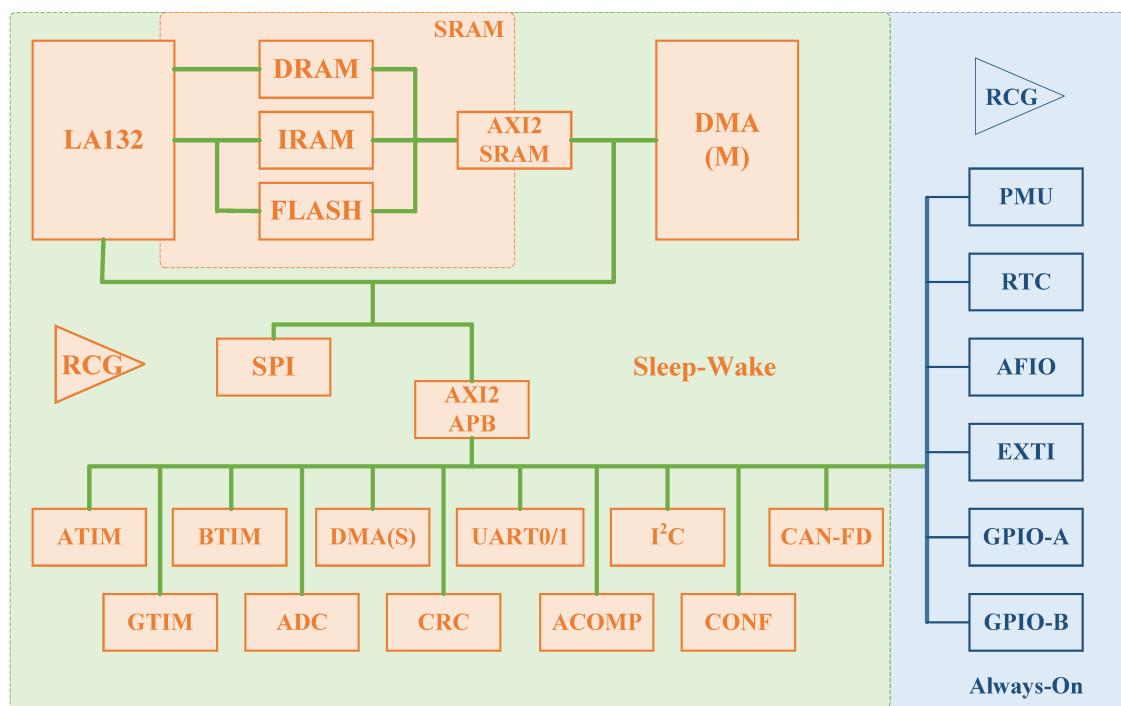

芯片以龙芯 LA132 处理器核为计算核心，采用 32 位 AXI+APB 两级总线连接片上资源和外围接口。芯片的结构如图1.1所示。

图 1.1: 龙芯 1C203 结构图

## 1.3 文档约定

### 1.3.1 信号命名

信号名的选取以方便记忆和明确标识功能为原则。低有效信号以 n 结尾，高有效信号则不带 n。

### 1.3.2 信号类型

表 1.1: 信号类型约定

| 代码       | 描述   |

|----------|------|

| A        | 模拟   |

| DIFF I/O | 双向差分 |

| DIFF I   | 差分输入 |

| DIFF O   | 差分输出 |

| I        | 输入   |

| I/O      | 双向   |

| O        | 输出   |

| OD       | 开漏输出 |

| P        | 电源   |

| G        | 地    |

### 1.3.3 数值表示

16 进制数表示为 'hxx, 2 进制数表示为 'bxx, 其他数字为 10 进制数。

### 1.3.4 寄存器域

寄存器域以 [寄存器名].[域名] 的形式加以引用。如 ChipCtrl.input\_hold 指芯片配置寄存器 (ChipCtrl) 的 input\_hold 域。

## 第二章 地址空间

表 2.1: 地址空间分布

| 地址空间                      | 模块               | 说明                   | 访问  |

|---------------------------|------------------|----------------------|-----|

| 0x0000_1000 - 0x0000_10ff | ATIM             | 高级定时器                | W   |

| 0x0000_2000 - 0x0000_20ff | GTIM             | 通用定时器                | W   |

| 0x0000_3000 - 0x0000_30ff | BTIM             | 基础定时器                | W   |

| 0x0000_4000 - 0x0000_40ff | ADC              | ADC 控制器              | W   |

| 0x0000_5000 - 0x0000_50ff | DMA              | DMA 控制器              | W   |

| 0x0000_6000 - 0x0000_60ff | CRC              | CRC 控制器              | W   |

| 0x0000_7000 - 0x0000_70ff | Flash            | Flash 控制器            | W   |

| 0x0000_8000 - 0x0000_80ff | SPI              | SPI 控制器              | W   |

| 0x0000_9000 - 0x0000_90ff | UART0            | 串口 0 控制器             | W   |

| 0x0000_9100 - 0x0000_91ff | UART1            | 串口 1 控制器             | W   |

| 0x0000_a000 - 0x0000_a0ff | I <sup>2</sup> C | I <sup>2</sup> C 控制器 | W   |

| 0x0000_b000 - 0x0000_b0ff | CONFREG          | CONF 控制器             | W   |

| 0x0000_c000 - 0x0000_c0ff | PMU              | 电源管理单元               | W   |

| 0x0000_c800 - 0x0000_c8ff | RTC              | 实时时钟                 | W   |

| 0x0000_d000 - 0x0000_d0ff | AFIO             | 管脚复用控制器              | W   |

| 0x0000_d100 - 0x0000_d1ff | EXTI             | 外部中断控制器              | W   |

| 0x0000_d200 - 0x0000_d2ff | GPIOA            | GPIOA 控制器            | BW  |

| 0x0000_d300 - 0x0000_d3ff | GPIOB            | GPIOA 控制器            | BW  |

| 0x0000_e000 - 0x0000_e0ff | CAN              | CAN 控制器              | W   |

| 0x0000_f000 - 0x0000_f0ff | ACOMP            | ACOMP 控制器            | W   |

| 0x1000_0000 - 0x1000_1fff | IRAM             | 8KB, 可取指             | BHW |

| 0x1000_2000 - 0x1000_3fff | DRAM             | 8KB, 可取指             | BHW |

| 0x1800_0000 - 0x1801_ffff | Flash            | Flash 存储区            | BHW |

| 0x1c00_0000 - 0x1fff_ffff | Boot             | 启动存储区映射              | BHW |

| 0x2000_0000 - 0x2fff_ffff | SPI              | SPI Flash 存储区        | BHW |

注 1 : 访问类型包括字节 (B)、半字 (H) 和字 (W), 访存地址必须对齐。

## 第三章 ATIM 定时器

### 3.1 概述

龙芯 1C203 提供了一个由单个 16 位自动装载计数器驱动的 ATIM。

它适用于多种应用，如测量输入信号的脉冲长度或产生指定的输出波形。同时 ATIM 具有三路互补输出通道，对于电机相关应用具有良好的支持。

ATIM 的时钟由内部 APB 总线时钟提供，地址为 0x00001000，寄存器定义见下文。

### 3.2 功能描述

#### 3.2.1 计数模式

定时器具有向上、向下、中央对齐 3 种计数模式，其中单向计数模式与中央对齐模式通过 CR1 寄存器中的 CMS 配置位进行选择。在单向计数模式中，用户通过配置 CR1 寄存器中的 DIR 位选择向上/向下计数。在中央对齐模式中，DIR 位只读，由硬件自动设置用于指示当前的计数方向。

用户可通过配置 PSC 寄存器对计数器时钟进行预分频，配置 ARR 寄存器用于配置计数周期，且可对 CNT 计数器实时进行读取与修改，实际完成一次计数周期的时长由 PSC 与 ARR 共同决定。

PSC 与 ARR 寄存器具有预装载功能，即当次的配置值会留到下个计数周期/更新事件产生时才生效，其中 PSC 寄存器预装载功能始终打开，ARR 寄存器预装载功能可自由选择开启或关闭。

ATIM 模块中 CNT 的计数时钟默认由内部 APB 总线时钟提供，用户也可以通过配置 SMCR 寄存器以使用外部输入的脉冲信号或芯片内部互联信号来进行计数，以实现更灵活的应用。

每次计数器溢出、设置 UG 位、从模式控制器产生硬件复位时可根据相关配置位配置产生更新事件。

ATIM 中具有重复计数模式。通过配置重复计数器，可以让用户控制在每 N 次计数上溢或下溢时产生一次更新事件，其中 N 为 RCR 重复计数寄存器中的值。重复计数器在任意模式下计数器发生上溢/下溢时计数。重复计数器始终开启预装载。

当发生更新事件时，PSC 内部计数被清零，CNT 根据计数模式进行重装载，同时：

- SR 寄存器中的 UIF 标志位被设置。

- PSC 与 RCR 寄存器中的值被装载到实际的内部寄存器。

- 若设置了 ARPE 位，ARR 寄存器中的值被装载到实际的自动重装载寄存器。

通过设置 CR1 寄存器中的 UDIS 位，可以禁止除写入 UG 位外的更新事件产生。如设置了 CR1 寄存器中的 URS 位，通过设置 EGR 寄存器中的 UG 位可以手动产生一个更新事件，但不设置 UIF 标志位。

### 3.2.2 输入模式

ATIM 具有 4 个独立的输入/输出通道，每个通道都可独立地选择输入/输出模式，但同一个通道同时只能选择输入或输出模式中的一种。

由于 4 个通道共用同个 CNT 计数器，因此在使用时需要注意计数值的耦合关系。在输出模式下使用从模式中的复位模式配合进行 PWM 频率捕获时，需要注意仅指定的外部模块输入、CH11、CH2、ETR 信号可用于 CNT 计数器复位，CH3、CH4 信号无法用于计数复位。

在输入模式下，当检测到 CHx 信号上相应的边沿后，计数器的当前值被锁存到捕获/比较寄存器（CCRx）中。当捕获事件发生时，SR 寄存器中相应通道的 CCxIF 标志被置 '1'，如果在 DIER 中使能了相应的中断或 DMA，则将产生中断或 DMA 请求。如果捕获事件发生时 CCxIF 标志已经为 '1'，那么 SR 寄存器中的重复捕获标志 CCxOF 标志将被置 '1'，该标志有助于用户判断是否存在被错过的捕获事件。

写 CCxIF=0 可清除 CCxIF，或读取存储在对应通道的 CCRx 寄存器中的数据也可清除 CCxIF。写 CCxOF=0 可清除 CCxOF。

注：设置 EGR 寄存器中相应的 CCxG 位，可以通过软件输入产生输入捕获事件，同时根据 DIER 寄存器的配置产生中断或 DMA 请求。

#### 3.2.2.1 编码器接口模式

编码器接口模式是输入模式下的一种特殊应用，可连接外部增量式编码器用于计数。

两个输入 CH1 和 CH2 被用来作为增量编码器的接口。根据两个输入信号的跳变顺序，产生了计数脉冲和方向信号，计数器向上或向下计数，同时硬件对 CR1 寄存器的 DIR 位进行相应的设置。

选择编码器接口模式的方法是：如果计数器只在 CH2 的边沿计数，则置 SMCR 寄存器中的 SMS=001；如果只在 CH1 边沿计数，则置 SMS=010；如果计数器同时在 CH1 和 CH2 边沿计数，则置 SMS=011。

| 有效边沿            | 相对信号的电平 | CH1FP1 |      | CH2FP2 |      |

|-----------------|---------|--------|------|--------|------|

|                 |         | 上升     | 下降   | 上升     | 下降   |

| 仅在 CH1 计数       | 高       | 向下计数   | 向上计数 | 不计数    | 不计数  |

|                 | 低       | 向上计数   | 向下计数 | 不计数    | 不计数  |

| 仅在 CH2 计数       | 高       | 不计数    | 不计数  | 向上计数   | 向下计数 |

|                 | 低       | 不计数    | 不计数  | 向下计数   | 向上计数 |

| 在 CH1 和 CH2 上计数 | 高       | 向下计数   | 向上计数 | 向上计数   | 向下计数 |

|                 | 低       | 向上计数   | 向下计数 | 向下计数   | 向上计数 |

编码器接口模式在开始计数之前必须配置 ARR 与其他寄存器，其配置与通常的计数模式保持一致。

在这个模式下，计数器依照增量编码器的速度和方向被自动的修改，因此计数器的内容始终指示着编码器的位置。计数方向与相连的传感器旋转的方向对应。

### 3.2.2.2 霍尔传感器模式

定时器为外部霍尔传感器应用进行优化。通过配置 CR2 寄存器中的 TIIS 位，可将 CH1、CH2、CH3 输入引脚或后作为通道 1 输入，因此外部霍尔传感器的所有边沿均可通过通道 1 触发内部中断，进而读取外部霍尔传感器输入电平确定转子位置，完成换相配置。

### 3.2.3 输出模式

该功能用于控制一个输出波形，或者通过电平变化指示时间的变化。

其中通道 1-3 具有互补输出通道。在输出模式下捕获/比较寄存器可开启预装载功能。

#### 3.2.3.1 电平输出模式

当计数器 CNT 与 CCRx 寄存器的值相同时，即称为发生比较匹配事件，此时 OCxREF 信号根据所配置的输出模式，可以保持原本电平 (OCxM=000)、被设置为有效电平 (OCxM=001)、被设置为无效电平 (OCxM=010)、始终输出低电平 (OCxM=0x100)、始终输出高电平 (OCxM=0x101) 或将当前电平状态进行翻转 (OCxM=011)，再根据 CCER 寄存器中 CCxP 输出极性配置，将符合期望的值输出到对应的引脚上。同时 SR 寄存器中对应的 CCxFIF 标志位被设置，并根据 DIER/CR2 寄存器相关配置产生中断或 DMA 请求。

例如：配置 OC1M=101,CC1P=0，即可强制 OC1 输出高电平。

### 3.2.3.2 PWM 模式

脉冲宽度调制模式可以产生一个由 ARR 寄存器确定频率、由 CCRx 寄存器确定占空比的信号。

在 CCMRx 寄存器中的 OCxM 位写入 '110'(PWM 模式 1) 或 '111'(PWM 模式 2), 能够独立地设置每个 OCx 输出通道产生一路 PWM。用户可设置 CCMRx 寄存器 OCxPE 位以使能相应的预装载寄存器。

仅当发生一个更新事件的时候, 被配置为预装载模式的寄存器中的配置值才可生效, 因此在计数器开始计数之前, 必须通过设置 EGR 寄存器中的 UG 位来初始化所有的寄存器。

CCER 寄存器中的 CCxP/CCxE 位控制 OCx 输出极性与使能。

根据 CR1 寄存器中 CMS 位的状态, 定时器能够产生边沿对齐的 PWM 信号或中央对齐的 PWM 信号。

当 CR1 寄存器中的 DIR 位为低的时候执行向上计数。以 PWM 模式 1 为例, 当 CNT<CCRx 时 PWM 信号参考 OCxREF 为高, 否则为低。如果 CCRx 中的比较值大于自动重装载值 (ARR), 则 OCxREF 保持为 '1'。如果 CCRx 中的比较值为 0, 则 OCxREF 保持为 '0'。

当 CR1 寄存器的 DIR 位为高时执行向下计数。在 PWM 模式 1 时, 当 CNT>CCRx 时参考信号 OCxREF 为低, 否则为高。如果 CCRx 中的比较值大于 ARR 中的自动重装载值, 则 OCxREF 保持为 '1'。该模式下不能产生占空比为 0

**在外部事件时清除 OCxREF 信号**对于一个给定的通道, 设置 CCMRx 寄存器中对应的 OCxCE 位为 '1', 能够用 ETRF 输入端的高电平把 OCxREF 信号拉低, OCxREF 信号将保持为低直到发生下一次的更新事件 UEV。该功能只能用于输出比较和 PWM 模式, 而不能用于强置模式。

#### 单脉冲模式

将 CR1 寄存器中的 OPM 位置为 '1' 将选择单脉冲模式, 这样可以让定时器自动地在产生下一个更新事件 UEV 时清除 CEN 位, 从而停止计数。这种模式可用于让定时器响应一个激励, 并在一个程序可控的延时之后, 产生一个脉宽可程序控制的脉冲。

### 3.2.3.3 互补输出和死区插入

ATIM 的 CH1-CH3 通道可以输出两路互补信号, 并且能够在互补信号中插入用户可配置的死区时间。每个互补通道都有一个 10 位的死区发生器, 参考信号 OCxREF 可以产生两路输出 OCx 和 OCxN, 且可为每一个输出独立选择极性。如果 OCx 和 OCxN 均为高有效:

- OCx 输出信号与参考信号相同，只是其上升沿相对于参考信号的上升沿有一个延迟

- OCxN 输出信号与参考信号相反，只是其上升沿相对于参考信号的下降沿有一个延迟

若延迟大于当前有效的输出宽度，则不会产生相应的脉冲。

各通道的死区延迟都是相同的，通过 BDTR 寄存器中的 DTG 位配置。

#### 重定向 OCxREF 到 OCx 或 OCxN

在输出模式下，通过配置 CCER 寄存器的 CCxE 位和 CCxNE 位，OCxREF 可以被重定向到 OCx 或 OCxN 的输出。当只使能 OCx 或只使能 OCxN 时，OCxREF 直接被连接到 OCx 或 OCxN。当 OCx 与 OCxN 都被使能时，OCxREF 先经过互补输出与死区插入控制模块，产生带有死区的互补信号，再分别连接到 OCx 与 OCxN。

#### 3.2.3.4 刹车输入

通过设置 BDTR 寄存器中的 BKE 位和 BKP 位可以使能刹车功能与选择刹车输入信号的极性。当在刹车输入端出现选中的电平时，产生一个刹车事件，MOE 位被清除，将输出关闭。同时若配置了 DIER 寄存器中的 BIE 位，则产生一个中断。

如果设置了 BDTR 寄存器中的 AOE 位，则在下一个更新事件产生时，MOE 被自动置位。

#### 3.2.4 定时器外部控制

通过配置 SMCR 寄存器中的 SMS 位，可使用外部信号对定时器进行一定程度的控制。

### 3.3 寄存器空间

表 3.1: ATIM 控制器寄存器列表

| 名称    | 偏移   | 描述           |

|-------|------|--------------|

| CR1   | 0x00 | 控制寄存器 1      |

| CR2   | 0x04 | 控制寄存器 2      |

| SMCR  | 0x08 | 从模式控制寄存器     |

| DIER  | 0x0c | DMA/中断使能寄存器  |

| SR    | 0x10 | 状态寄存器        |

| EGR   | 0x14 | 事件产生寄存器      |

| CCMR1 | 0x18 | 捕获/比较模式寄存器 1 |

| CCMR2 | 0x1c | 捕获/比较模式寄存器 2 |

| CCER  | 0x20 | 捕获/比较使能寄存器   |

| 名称    | 偏移   | 描述         |

|-------|------|------------|

| CNT   | 0x24 | 计数器        |

| PSC   | 0x28 | 预分频器       |

| ARR   | 0x2c | 自动重装载寄存器   |

| RCR   | 0x30 | 重复计数寄存器    |

| CCR1  | 0x34 | 捕获/比较寄存器 1 |

| CCR2  | 0x38 | 捕获/比较寄存器 2 |

| CCR3  | 0x3c | 捕获/比较寄存器 3 |

| CCR4  | 0x40 | 捕获/比较寄存器 4 |

| BDTR  | 0x44 | 刹车和死区寄存器   |

| INSTA | 0x50 | 输入通道状态寄存器  |

### 3.3.1 控制寄存器 1 (CR1)

偏 移: 0x00

复位值: 32'h0

表 3.2: 控制寄存器 1

| 位域    | 名称       | 访问 | 描述                                                                                                                                                                                                                                               |

|-------|----------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:10 | reserved | -  | 保留                                                                                                                                                                                                                                               |

| 9:8   | CKD[1:0] | RW | <b>时钟分频因子</b><br>配置定时器时钟频率 $CK\_APB$ 与数字滤波器使用的采样频率之间的分频关系<br>00: $t_{DTS} = t_{APB}$<br>01: $t_{DTS} = 2 \times t_{APB}$<br>10: $t_{DTS} = 4 \times t_{APB}$<br>11: 保留                                                                           |

| 7     | ARPE     | RW | <b>自动重装载预装载使能</b><br>0:ARR 寄存器没有预装载<br>1:ARR 寄存器开启预装载                                                                                                                                                                                            |

| 6:5   | CMS[1:0] | RW | <b>计数模式选择</b><br>00: 边沿对齐模式。计数器依据方向位 (dir) 向上或向下计数。<br>01: 中央对齐模式 1。计数器交替地向上或向下计数。配置为输出的通道的输出比较标志位，只在计数器向下计数时被设置。<br>10: 中央对齐模式 2。计数器交替地向上或向下计数。配置为输出的通道的输出比较标志位，只在计数器向上计数时被设置。<br>11: 中央对齐模式 3。计数器交替地向上或向下计数。配置为输出的通道的输出比较标志位，在计数器向上和向下计数时均被设置。 |

| 4     | DIR      | RW | <b>方向</b><br>0: 计数器向上计数<br>1: 计数器向下计数<br>注: 当计数器配置为中央对齐模式或编码器模式时，该位由硬件自动配置，只读                                                                                                                                                                    |

| 3     | OPM      | RW | <b>单脉冲模式</b><br>0: 关闭单脉冲模式<br>1: 发生更新事件时，清除 CEN 位，停止计数                                                                                                                                                                                           |

| 位域 | 名称   | 访问 | 描述                                                                                                                                                                 |

|----|------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | URS  | RW | <b>更新请求源</b><br>0: 计数器上溢或下溢、设置 UG 位、通过从模式控制器产生的更新均可产生更新中断或 DMA 请求<br>1: 只有计数器上溢或下溢可以产生更新中断或者 DMA 请求                                                                |

| 1  | UDIS | RW | <b>禁止更新</b><br>0: 计数器上溢或下溢、设置 UG 位、通过从模式控制器产生的更新可产生更新事件。产生更新事件后，开启预装载的寄存器被加载为预装载值。<br>1: 禁止更新事件产生。此时开启预装载的寄存器将保持其内容无法被更改，但通过设置 UG 位或从模式控制器产生了硬件复位，计数器和预分频器将被重新初始化。 |

| 0  | CEN  | RW | <b>计数使能</b><br>0: 停止计数<br>1: 使能计数                                                                                                                                  |

### 3.3.2 控制寄存器 2 (CR2)

偏 移: 0x04

复位值: 32'h0

表 3.3: 控制寄存器 2

| 位域    | 名称       | 访问 | 描述                                                                                                                                                                  |

|-------|----------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:15 | reserved | -  | 保留                                                                                                                                                                  |

| 14    | IOS4     | RW | <b>空闲输出状态 4</b><br>参见 IOS1 位                                                                                                                                        |

| 13    | IOS3N    | RW | <b>互补空闲输出状态 3</b><br>参见 IOSIN 位                                                                                                                                     |

| 12    | IOS3     | RW | <b>空闲输出状态 3</b><br>参见 IOS1 位                                                                                                                                        |

| 11    | IOS2N    | RW | <b>互补空闲输出状态 2</b><br>参见 IOSIN 位                                                                                                                                     |

| 10    | IOS2     | RW | <b>空闲输出状态 2</b><br>参见 IOS1 位                                                                                                                                        |

| 9     | IOSIN    | RW | <b>互补空闲输出状态 1</b><br>0: 当 MOE=0 且 OSI=1 时，则死区后 OCIN=0<br>1: 当 MOE=0 且 OSI=1 时，则死区后 OCIN=1<br>注 1: 为安全起见，当 IOS1 与 IOSIN 同时为 1 时，OC1=OCIN=0<br>注 2: 只有当 OSI=1 时该控制位生效 |

| 8     | IOS1     | RW | <b>空闲输出状态 1</b><br>0: 当 MOE=0 且 OSI=1 时，则死区后 OC1=0<br>1: 当 MOE=0 且 OSI=1 时，则死区后 OC1=1                                                                               |

| 7     | TIIS     | RW | <b>TI1 输入选择</b><br>0:CH1 引脚连接到 TI1 输入<br>1:CH1、CH2、CH3 引脚经异或后连到 TI1 输入                                                                                              |

| 位域  | 名称       | 访问 | 描述                                                                                                                                                                                                                                                                                                                                               |

|-----|----------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4 | MMS[2:0] | RW | <b>主模式选择</b><br>该配置位用于选择在主模式下向从外设发送的触发输出来源。<br>000: 复位 - 使用配置 UG 位和从模式控制器产生的硬件复位作为触发输出。<br>001: 使能 - 使用计数器使能信号作为触发输出。计数器实际使能信号由 CEN 控制位与门控模式下触发输入共同决定。<br>010: 更新 - 更新事件作为触发输出。<br>011: 比较脉冲 - 当发生一次捕获或比较成功时，当要设置 CCIF 标志时(即使已经为高)，触发输出一个脉冲。<br>100:OC1REF 信号被作为触发输出。<br>101:OC2REF 信号被作为触发输出。<br>110:OC3REF 信号被作为触发输出。<br>111:OC4REF 信号被作为触发输出。 |

| 3   | CCDS     | RW | <b>捕获/比较的 DMA 选择</b><br>0: 当发生比较/捕获事件时，发送 CCx 的 DMA 请求<br>1: 当发生更新事件时，发送 CCx 的 DMA 请求                                                                                                                                                                                                                                                            |

| 2   | CCUS     | RW | <b>捕获/比较控制更新选择</b><br>0: 如果捕获/比较控制位是预装载的 (CCPC=1)，只能通过设置 COM 位被更新<br>1: 如果捕获/比较控制位是预装载的 (CCPC=1)，可以通过设置 COM 位或在 TRGI 上发生触发输入时更新                                                                                                                                                                                                                  |

| 1   | reserved | -  | 保留                                                                                                                                                                                                                                                                                                                                               |

| 0   | CCPS     | RW | <b>捕获/比较预装载控制</b><br>0:CCxE,CCxNE 和 OCxM 位不是预装载的<br>1:CCxE,CCxNE 和 OCxM 位是预装载的，设置该位后，只有在满足 CCUS 位条件的事件发生时才会被更新<br>注: 该位只对具有互补输出的通道有效                                                                                                                                                                                                             |

### 3.3.3 从模式控制寄存器 (SMCR)

偏 移: 0x08

复位值: 32'h0

表 3.4: 从模式控制寄存器

| 位域    | 名称       | 访问 | 描述                                                                                                                                                 |

|-------|----------|----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 3l:16 | reserved | -  | 保留                                                                                                                                                 |

| 15    | ETP      | RW | <b>外部触发极性</b><br>0:ETR 不反相<br>1:ETR 反相                                                                                                             |

| 14    | ECE      | RW | <b>外部时钟使能位</b><br>0: 禁止外部时钟模式 2<br>1: 使能外部使能模式 2<br>注: 复位模式、门控模式和触发模式可以与外部时钟模式 2 同时使用，但是此时 TRGI 不能连接到 ETR。当外部时钟模式 1 和外部时钟模式 2 同时被使能时，外部时钟的输入是 ETR。 |

| 位域    | 名称       | 访问 | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:12 | reserved | -  | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11:8  | ETF[3:0] | RW | <p><b>外部触发滤波</b></p> <p>配置对 ETR 信号采样的频率和数字滤波的带宽。数字滤波器是一个事件计数器，记录到 N 个事件后产生输出跳变。</p> <p>0000: 无滤波器，以 <math>f_{DTS}</math> 采样<br/>     0001: 采样频率 <math>f_{SAMP} = f_{APB}</math>, N=2<br/>     0010: 采样频率 <math>f_{SAMP} = f_{APB}</math>, N=4<br/>     0011: 采样频率 <math>f_{SAMP} = f_{APB}</math>, N=8<br/>     0100: 采样频率 <math>f_{SAMP} = f_{DTS}/2</math>, N=6<br/>     0101: 采样频率 <math>f_{SAMP} = f_{DTS}/2</math>, N=8<br/>     0110: 采样频率 <math>f_{SAMP} = f_{DTS}/4</math>, N=6<br/>     0111: 采样频率 <math>f_{SAMP} = f_{DTS}/4</math>, N=8<br/>     1000: 采样频率 <math>f_{SAMP} = f_{DTS}/8</math>, N=6<br/>     1001: 采样频率 <math>f_{SAMP} = f_{DTS}/8</math>, N=8<br/>     1010: 采样频率 <math>f_{SAMP} = f_{DTS}/16</math>, N=5<br/>     1011: 采样频率 <math>f_{SAMP} = f_{DTS}/16</math>, N=6<br/>     1100: 采样频率 <math>f_{SAMP} = f_{DTS}/16</math>, N=8<br/>     1101: 采样频率 <math>f_{SAMP} = f_{DTS}/32</math>, N=5<br/>     1110: 采样频率 <math>f_{SAMP} = f_{DTS}/32</math>, N=6<br/>     1111: 采样频率 <math>f_{SAMP} = f_{DTS}/32</math>, N=8</p> |

| 7     | TSYN     | RW | <p><b>触发同步</b></p> <p>0: 关闭主从模式<br/>     1: 触发输入上的事件被延迟触发，从而让当前定时器与被它的触发输出所控制的从定时器间达成同步</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6:4   | TS[2:0]  | RW | <p><b>触发来源选择</b></p> <p>000: 内部触发 0,GTIM<br/>     001-011: 保留<br/>     100:TII 的边沿检测器<br/>     101: 滤波后的 CH1 输入<br/>     110: 滤波后的 CH2 输入<br/>     111: 外部触发输入 ETR</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3     | reserved | -  | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 位域  | 名称       | 访问 | 描述                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|----------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0 | SMS[2:0] | RW | <b>从模式选择</b><br>000: 关闭从模式<br>001: 编码器模式 1-根据 TI1 的电平, 计数器在 TI2 的边沿向上/向下计数<br>010: 编码器模式 2-根据 TI2 的电平, 计数器在 TI1 的边沿向上/向下计数<br>011: 编码器模式 3-根据另一个信号的电平, 计数器在 TI1 和 TI2 的边沿向上/向下计数<br>100: 复位模式 -在选中的触发输入 (TRGI) 的上升沿初始化计数器, 并产生一个更新寄存器的信号<br>101: 门控模式 -当触发输入为高时, 计数器计数; 当触发输入为低时, 计数器停止计数但不复位。仅 CEN 位为 '1' 时门控模式有效<br>110: 触发模式 -在触发输入的上升沿, CEN 位被硬件设置为 '1'<br>111: 外部时钟模式 1-在选中的触发输入的上升沿, 计数器计数 |

### 3.3.4 DMA/中断使能寄存器 (DIER)

偏 移: 0x0c

复位值: 32'h0

表 3.5: DMA/中断使能寄存器

| 位域    | 名称       | 访问 | 描述                                                                                |

|-------|----------|----|-----------------------------------------------------------------------------------|

| 31:l5 | reserved | -  | 保留                                                                                |

| 14    | TDE      | RW | <b>触发事件 DMA 请求使能</b><br>0: 禁止触发事件 DMA 请求<br>1: 使能触发事件 DMA 请求                      |

| 13    | COMDE    | RW | <b>COM 事件 DMA 请求使能</b><br>0: 禁止 COM 事件 DMA 请求<br>1: 使能 COM 事件 DMA 请求              |

| 12    | CC4DE    | RW | <b>捕获/请求通道 4 的 DMA 请求使能</b><br>0: 禁止捕获/比较通道 4 的 DMA 请求<br>1: 使能捕获/比较通道 4 的 DMA 请求 |

| 11    | CC3DE    | RW | <b>捕获/请求通道 3 的 DMA 请求使能</b><br>0: 禁止捕获/比较通道 3 的 DMA 请求<br>1: 使能捕获/比较通道 3 的 DMA 请求 |

| 10    | CC2DE    | RW | <b>捕获/请求通道 2 的 DMA 请求使能</b><br>0: 禁止捕获/比较通道 2 的 DMA 请求<br>1: 使能捕获/比较通道 2 的 DMA 请求 |

| 9     | CC1DE    | RW | <b>捕获/请求通道 1 的 DMA 请求使能</b><br>0: 禁止捕获/比较通道 1 的 DMA 请求<br>1: 使能捕获/比较通道 1 的 DMA 请求 |

| 8     | UDE      | RW | <b>更新事件 DMA 请求使能</b><br>0: 禁止更新事件 DMA 请求<br>1: 使能更新事件 DMA 请求                      |

| 位域 | 名称    | 访问 | 描述                                                               |

|----|-------|----|------------------------------------------------------------------|

| 7  | BIE   | RW | <b>刹车事件中断使能</b><br>0: 禁止刹车事件中断<br>1: 使能刹车事件中断                    |

| 6  | TIE   | RW | <b>触发事件中断使能</b><br>0: 禁止触发事件中断<br>1: 使能触发事件中断                    |

| 5  | COMIE | RW | <b>COM 事件中断使能</b><br>0: 禁止 COM 事件中断<br>1: 使能 COM 事件中断            |

| 4  | CC4IE | RW | <b>捕获/请求通道 4 的中断使能</b><br>0: 禁止捕获/比较通道 4 中断<br>1: 使能捕获/比较通道 4 中断 |

| 3  | CC3IE | RW | <b>捕获/请求通道 3 的中断使能</b><br>0: 禁止捕获/比较通道 3 中断<br>1: 使能捕获/比较通道 3 中断 |

| 2  | CC2IE | RW | <b>捕获/请求通道 2 的中断使能</b><br>0: 禁止捕获/比较通道 2 中断<br>1: 使能捕获/比较通道 2 中断 |

| 1  | CCIIE | RW | <b>捕获/请求通道 1 的中断使能</b><br>0: 禁止捕获/比较通道 1 中断<br>1: 使能捕获/比较通道 1 中断 |

| 0  | UIE   | RW | <b>更新事件中断使能</b><br>0: 禁止更新事件中断<br>1: 使能更新事件中断                    |

### 3.3.5 状态寄存器 (SR)

偏 移: 0x10

复位值: 32'h0

表 3.6: 状态寄存器

| 位域    | 名称       | 访问       | 描述                                                                                 |

|-------|----------|----------|------------------------------------------------------------------------------------|

| 3l:13 | reserved | -        | 保留                                                                                 |

| 12    | CC4OF    | RC<br>W0 | <b>捕获/请求通道 4 重复捕获事件标志位</b><br>仅当相应通道被配置为输入捕获时有意义<br>0: 无重复捕获事件<br>1: 通道 4 发生重复捕获事件 |

| 11    | CC3OF    | RC<br>W0 | <b>捕获/请求通道 3 重复捕获事件标志位</b><br>0: 无重复捕获事件<br>1: 通道 3 发生重复捕获事件                       |

| 10    | CC2OF    | RC<br>W0 | <b>捕获/请求通道 2 重复捕获事件标志位</b><br>0: 无重复捕获事件<br>1: 通道 2 发生重复捕获事件                       |

| 9     | CC1OF    | RC<br>W0 | <b>捕获/请求通道 1 重复捕获事件标志位</b><br>0: 无重复捕获事件<br>1: 通道 1 发生重复捕获事件                       |

| 位域 | 名称       | 访问       | 描述                                                                                                                     |

|----|----------|----------|------------------------------------------------------------------------------------------------------------------------|

| 8  | reserved | -        | 保留                                                                                                                     |

| 7  | BIF      | RC<br>W0 | <b>刹车事件标志位</b><br>硬件在产生刹车事件发生时设置该位，软件写 0 清除<br>0: 未产生刹车事件<br>1: 产生了刹车事件                                                |

| 6  | TIF      | RC<br>W0 | <b>触发事件标志位</b><br>当发生触发事件（当从模式控制器处于除门控模式外的其他模式在触发输入端检测到有效边沿，或门控模式下任一边沿）时硬件置 '1'，软件写 '0' 清除。<br>0: 无触发事件发生<br>1: 发生触发事件 |

| 5  | COMIF    | RC<br>W0 | <b>COM 事件标志位</b><br>硬件在产生 COM 事件发生时设置该位，软件写 0 清除<br>0: 未产生 COM 事件<br>1: 产生了 COM 事件                                     |

| 4  | CC4IF    | RC<br>W0 | <b>捕获/请求通道 4 事件标志位</b><br>0: 无捕获/比较事件<br>1: 通道 4 发生捕获/比较通道事件                                                           |

| 3  | CC3IF    | RC<br>W0 | <b>捕获/请求通道 3 事件标志位</b><br>0: 无捕获/比较事件<br>1: 通道 3 发生捕获/比较通道事件                                                           |

| 2  | CC2IF    | RC<br>W0 | <b>捕获/请求通道 2 事件标志位</b><br>0: 无捕获/比较事件<br>1: 通道 2 发生捕获/比较通道事件                                                           |

| 1  | CCIIF    | RC<br>W0 | <b>捕获/请求通道 1 事件标志位</b><br>0: 无捕获/比较事件<br>1: 通道 1 发生捕获/比较通道事件                                                           |

| 0  | UIF      | RC<br>W0 | <b>更新事件标志位</b><br>硬件在产生更新事件时设置该位，软件写 0 清除<br>0: 未产生更新事件<br>1: 产生了更新事件                                                  |

### 3.3.6 事件产生寄存器 (EGR)

偏 移: 0x14

复位值: 32'h0

表 3.7: 事件产生寄存器

| 位域   | 名称       | 访问 | 描述                                       |

|------|----------|----|------------------------------------------|

| 31:8 | reserved | -  | 保留                                       |

| 7    | BG       | W  | <b>产生刹车事件</b><br>该位始终读为 0, 写 1 产生触发事件    |

| 6    | TG       | W  | <b>产生触发事件</b><br>该位始终读为 0, 写 1 产生触发事件    |

| 5    | COMG     | W  | <b>产生 COM 事件</b><br>该位始终读为 0, 写 1 产生触发事件 |

| 位域 | 名称   | 访问 | 描述                                                                                                                                                                                  |

|----|------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4  | CC4G | W  | <b>产生捕获/比较 4 事件</b><br>该位始终读为 0, 写 1 产生捕获/比较事件。<br>若通道为输出: 设置 CCIF 为 1, 若开启对应的中断和 DMA, 则产生相应的中断和 DMA<br>若通道为输入: 将当前计数器 CNT 的值捕获置 CCR1 寄存器, 设置 CCIF 为 1, 若 CCIF 已经为 1, 则设置 CCIOF 为 1 |

| 3  | CC3G | W  | <b>产生捕获/比较 3 事件</b><br>该位始终读为 0, 写 1 产生捕获/比较事件                                                                                                                                      |

| 2  | CC2G | W  | <b>产生捕获/比较 2 事件</b><br>该位始终读为 0, 写 1 产生捕获/比较事件                                                                                                                                      |

| 1  | CC1G | W  | <b>产生捕获/比较 1 事件</b><br>该位始终读为 0, 写 1 产生捕获/比较事件                                                                                                                                      |

| 0  | UG   | W  | <b>产生更新事件</b><br>该位始终读为 0, 写 1 产生更新事件, 初始化计数器并更新带有预装载的寄存器                                                                                                                           |

### 3.3.7 捕获/比较模式寄存器 1(输出) (CCMR1)

偏 移: 0x18

复位值: 32'h0

通道可用于输入捕获模式或输出比较模式, 通道的方向由相应的 CCxS 配置位定义。该寄存器其他位在输入和输出模式下不同, 同一个位在输入和输出模式下的意义是不同的。

表 3.8: 捕获/比较模式寄存器 1(输出)

| 位域    | 名称       | 访问 | 描述                                                              |

|-------|----------|----|-----------------------------------------------------------------|

| 31:16 | reserved | -  | 保留                                                              |

| 15    | OC2CE    | RW | <b>输出比较 2 清零使能</b><br>0: 无影响<br>1: 一旦检测到 ETR 输入高电平, 清除 OC2REF=0 |

| 位域    | 名称        | 访问 | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-----------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14:12 | OC2M[2:0] | RW | <b>输出比较 2 模式</b><br>000: 冻结, OC2REF 保持当前状态不变<br>001: 当计数器 CNT 的值与捕获/比较寄存器 CCR2 相同时, 强制 OC2REF 为高电平<br>010: 当计数器 CNT 的值与捕获/比较寄存器 CCR2 相同时, 强制 OC2REF 为低电平<br>011: 当计数器 CNT 的值与捕获/比较寄存器 CCR2 相同时, 翻转 OC2REF 的电平<br>100: 强制 OC2REF 为低电平<br>101: 强制 OC2REF 为高电平<br>110: PWM 模式 1-在向上计数时, 一旦 CNT<CCR2, OC2REF 为高电平, 否则为低电平; 在向下计数时, 一旦 CNT>CCR2, OC2REF 为低电平, 否则为高电平。<br>111: PWM 模式 2-在向上计数时, 一旦 CNT<CCR2, OC2REF 为低电平, 否则为高电平; 在向下计数时, 一旦 CNT>CCR2, OC2REF 为高电平, 否则为低电平。 |

| 11    | OC2PE     | RW | <b>输出比较 2 预装载使能</b><br>0: 关闭 CCR2 寄存器的预装载功能<br>1: 开启 CCR2 寄存器的预装载功能                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10    | OC2FE     | RW | <b>输出比较 2 快速使能</b><br>0: 无影响<br>1: 仅在单脉冲模式下且通道配置为 PWM1/PWM2 模式时生效, 当开始计数时, 立即输出有效电平, OC2REF 电平此时与比较结果无关                                                                                                                                                                                                                                                                                                                                                               |

| 9:8   | CC2S[1:0] | RW | <b>输出/比较 2 选择</b><br>00:CC2 通道被配置为输出<br>01:CC2 通道被配置为输入, IC2 映射在 TI2 上<br>10:CC2 通道被配置为输入, IC2 映射在 TI1 上<br>11:CC2 通道被配置为输入, IC2 映射在 TRC 上                                                                                                                                                                                                                                                                                                                            |

| 7     | OC1CE     | RW | <b>输出比较 1 清零使能</b><br>0: 无影响<br>1: 一旦检测到 ETR 输入高电平, 清除 OC1REF=0                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6:4   | OC1M[2:0] | RW | <b>输出比较 1 模式</b><br>参见 OC2M 说明                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3     | OC1PE     | RW | <b>输出比较 1 预装载使能</b><br>0: 关闭 CCR1 寄存器的预装载功能<br>1: 开启 CCR1 寄存器的预装载功能                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2     | OC1FE     | RW | <b>输出比较 1 快速使能</b><br>参见 OC2FE 说明                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1:0   | CC1S[1:0] | RW | <b>输出/比较 1 选择</b><br>00:CCI 通道被配置为输出<br>01:CCI 通道被配置为输入, IC1 映射在 TI1 上<br>10:CCI 通道被配置为输入, IC1 映射在 TI2 上<br>11:CCI 通道被配置为输入, IC1 映射在 TRC 上                                                                                                                                                                                                                                                                                                                            |

## 3.3.8 捕获/比较模式寄存器 1(输入) (CCMR1)

偏 移: 0x18

复位值: 32'h0

表 3.9: 捕获/比较模式寄存器 1(输入)

| 位域    | 名称          | 访问 | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | reserved    | -  | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15:12 | IC2F[3:0]   | RW | <p><b>输入捕获 2 滤波器</b><br/>           配置对 TI2 输入信号采样的频率和数字滤波的带宽。数字滤波器是一个事件计数器，记录到 N 个事件后产生输出跳变。</p> <p>0000: 无滤波器，以 <math>f_{DTS}</math> 采样<br/>           0001: 采样频率 <math>f_{SAMP} = f_{APB}</math>, N=2<br/>           0010: 采样频率 <math>f_{SAMP} = f_{APB}</math>, N=4<br/>           0011: 采样频率 <math>f_{SAMP} = f_{APB}</math>, N=8<br/>           0100: 采样频率 <math>f_{SAMP} = f_{DTS}/2</math>, N=6<br/>           0101: 采样频率 <math>f_{SAMP} = f_{DTS}/2</math>, N=8<br/>           0110: 采样频率 <math>f_{SAMP} = f_{DTS}/4</math>, N=6<br/>           0111: 采样频率 <math>f_{SAMP} = f_{DTS}/4</math>, N=8<br/>           1000: 采样频率 <math>f_{SAMP} = f_{DTS}/8</math>, N=6<br/>           1001: 采样频率 <math>f_{SAMP} = f_{DTS}/8</math>, N=8<br/>           1010: 采样频率 <math>f_{SAMP} = f_{DTS}/16</math>, N=5<br/>           1011: 采样频率 <math>f_{SAMP} = f_{DTS}/16</math>, N=6<br/>           1100: 采样频率 <math>f_{SAMP} = f_{DTS}/16</math>, N=8<br/>           1101: 采样频率 <math>f_{SAMP} = f_{DTS}/32</math>, N=5<br/>           1110: 采样频率 <math>f_{SAMP} = f_{DTS}/32</math>, N=6<br/>           1111: 采样频率 <math>f_{SAMP} = f_{DTS}/32</math>, N=8</p> |

| 11:10 | IC2PSC[1:0] | RW | <p><b>输入捕获 2 预分频器</b><br/>           定义 CC2 输入 (IC2) 的预分频系数</p> <p>00: 无预分频<br/>           01: 每 2 个事件触发一次捕获<br/>           10: 每 4 个事件触发一次捕获<br/>           11: 每 8 个事件触发一次捕获</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9:8   | CC2S[1:0]   | RW | <p><b>输出/比较 2 选择</b><br/>           00:CC2 通道被配置为输出<br/>           01:CC2 通道被配置为输入, IC2 映射在 TI2 上<br/>           10:CC2 通道被配置为输入, IC2 映射在 TI1 上<br/>           11:CC2 通道被配置为输入, IC2 映射在 TRC 上</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7:4   | IC1F[3:0]   | RW | <p><b>输入捕获 1 滤波器</b><br/>           参考 IC2F 说明</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3:2   | IC1PSC[1:0] | RW | <p><b>输入捕获 1 预分频器</b><br/>           参考 IC2PSC 说明</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 位域  | 名称        | 访问 | 描述                                                                                                                                  |

|-----|-----------|----|-------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | CCIS[1:0] | RW | 输出/比较 1 选择<br>00:CCI 通道被配置为输出<br>01:CCI 通道被配置为输入, IC1 映射在 TI1 上<br>10:CCI 通道被配置为输入, IC1 映射在 TI2 上<br>11:CCI 通道被配置为输入, IC1 映射在 TRC 上 |

### 3.3.9 捕获/比较模式寄存器 2(输出) (CCMR2)

偏 移: 0x1c

复位值: 32'h0

通道可用于输入捕获模式或输出比较模式, 通道的方向由相应的 CCxS 配置位定义。该寄存器其他位在输入和输出模式下不同, 同一个位在输入和输出模式下的意义是不同的。

表 3.10: 捕获/比较模式寄存器 2(输出)

| 位域    | 名称        | 访问 | 描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-----------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | reserved  | -  | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |